# NAVIGATING HETEROGENEITY AND SCALABILITY IN MODERN CHIP DESIGN

Marcelo Orenes-Vera

A Dissertation

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

OF DOCTOR OF PHILOSOPHY

IN CANDIDACY FOR THE DEGREE

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

COMPUTER SCIENCE

ADVISER: PROFESSORS MARGARET MARTONOSI AND DAVID WENTZLAFF

May 2024

© Copyright by Marcelo Orenes-Vera, 2024.

All rights reserved.

#### Abstract

Computing systems have become ubiquitous in the modern world but their design is far from one-size-fits-all. From battery-powered devices to supercomputers, deployment requirements are a primary driver of heterogeneity in computer design. As modern systems rely on parallelism and specialization to achieve their performance and power goals, new challenges arise. The system's complexity grows with the number of distinct hardware modules, complicating the verification of correct and secure behavior. Moreover, expanding parallelization across more processing units (PUs) increases the pressure on the memory hierarchy and inter-PU network, which results in severe bottlenecks for applications traversing graph-like data structures with indirect memory accesses (IMAs). These challenges call for re-thinking software abstractions and hardware designs to achieve scalable and efficient systems, as well as introducing robust methodologies to ensure their correctness. My dissertation aims to tackle these challenges with three main thrusts.

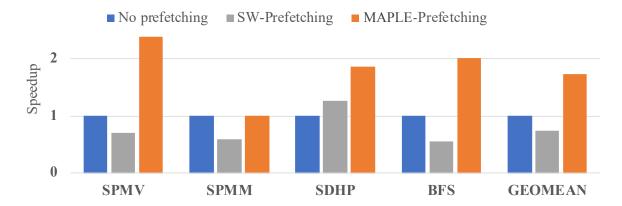

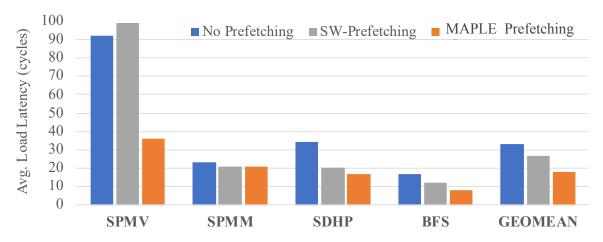

First, to facilitate hardware designers applying formal verification to their modules, this dissertation introduces AutoSVA, a toolflow that generates formal verification testbenches from module interface annotations. Testbenches generated with AutoSVA have uncovered bugs in open-source projects, including a widely used RISC-V CPU. Second, to alleviate IMA latency without increasing verification complexity, this dissertation introduces MAPLE, a network-connected memory-access engine that supports data pipelining and prefetching without requiring PU modifications. As such, off-the-shelf PUs can offload IMAs to MAPLE, and consume data via software-managed queues. Using MAPLE effectively mitigates memory latency, providing 2x speedups over software- and hardware-only prefetching. Third, to further the scalability of graph and sparse workloads, this dissertation co-designs scale-out architectures with a data-centric execution model, Dalorex, where IMAs are split into tasks that only access a confined address range and execute at the PU with dedicated access

to that memory range. The parallelization of breadth-first-search on a billion-edge graph across a million PUs results in nearly an order of magnitude faster runtimes than Graph500's top entries.

By introducing novel hardware designs, execution models, and verification tools, this dissertation contributes towards addressing the challenges posed by the increasing demand for high-performance, energy-efficient, and cost-effective computing systems.

#### Acknowledgements

During the journey that culminated in this dissertation, I have been fortunate to receive guidance, support, and inspiration from stellar people and institutions, whom I would like to thank here.

First and foremost, thank you to my advisers, Margaret Martonosi and David Wentzlaff, for all of your mentorship and support at every step of the way. Thank you Margaret for giving me the life-changing opportunity to come to Princeton to work with you, and for your incredibly valuable feedback and guidance. I am extremely grateful that you made time anytime I needed your help and advice even while being the director of NSF's CISE. Thank you David for your contagious enthusiasm and passion for advancing computer architecture. You encouraged me to think big, strive for impact, and always be curious and creative. Thank you for always being there, from discussing research ideas and deep technical questions to disconnecting and talking about skiing and mountains. Thank you again David and Margaret, being co-advised by both of you has been a unique and enriching experience. Your complementary expertise and perspectives have been instrumental in shaping my research and growth as a scholar.

Thank you to my dissertation committee members, Kai Li, Aarti Gupta, and Jonathan Balkind, I deeply appreciate your feedback on my work throughout my Ph.D. Thank you Kai for encouraging my research and for your teachings during the Systems and ML course. Thank you Aarti for your feedback on my work since my generals, and for your Automated Reasoning course, which inspired me to pursue research using formal methods. Thank you Jon, for everything. You have served several roles during my Princeton journey in addition to this committee, being a student mentor, a collaborator, and a friend. Thank you for all your help and support, from the early days of designing and debugging MAPLE, to the ups and downs

of a Ph.D. You shaped my graduate experience in many ways, among them, by encouraging me to serve as an RGS, for which I am hugely grateful.

Thank you to all the amazing researchers involved in the DECADES project. Thank you Luca Carloni, for your inspiring leadership in the open-source hardware community, and for supporting my academic aspirations. Thank you Tyler Sorensen, for being a role model during my first year at Princeton, and for your friendship and guidance throughout. Thank you Esin Tureci, for teaming up with me on Dalorex and beyond. Thank you for always being present and supportive, for your dedication, for staying up until the last minute during deadlines, and for your contagious excitement about Dalorex, which kept me going during tough times. I have been fortunate to have you as a collaborator and I am grateful for all the fun times we had working together. Thank you Aninda Manocha, for many research collaborations as well as fun adventures during our time at Princeton. Thank you Fei, Ang, Ting-Jung, Davide, and the rest of the DECADES team, for your hard work and dedication that made it a success. It was fascinating to work across the different layers of the stack, and I learned a lot from all of you.

Thank you to the MRMGroup students with whom I was fortunate to overlap, for all the fun times and adventures we had together, including a trip to Disney World, and many Karaoke nights. Even during the tough pandemic times, we managed to have fun and support each other, and I am grateful for that.

Thanks to all the Princeton Parallel Group students, for making the lab a very welcoming and fun place to work. I learned a lot from the unique technical expertise and experiences of each of you, and I am grateful for all the interactions we had over the years. Thank you to August for fostering the lab's culture, for being my travel mate in so many conferences, and for our amazing trip camping trip along the Appalachian mountains, I will never forget it. Thank you Grigory, Yebin, Rohan,

Hyunsung and Nils, for countless hours of research conversations as well as fun times and trips outside the lab, including fantastic trips in Europe.

Thank you Princeton for having such a wonderful residential graduate student program, and particularly, thank you to the staff of First College and NCW for creating a welcoming and inclusive environment that made Princeton feel like home. Thank you AnneMarie Luijendijk and Anne Caswell, for your contagious happiness and for always being there to help Katriina and me. Thank you to the college students, who via countless meals and interactions, helped me grow and become a better mentor.

I believe a key ingredient to success in graduate school is having a supportive and enriching community, and I am grateful to have found that at Princeton. Thank you to the GSG, GCHC, Davis IC, for organizing the events that brought us together, and thank you to the Blue House residents, for being a much-needed moral support during the first year and beyond. Keep the good vibes going!

Thank you to all the Princeton students and research peers I have met over these last five years, for making my doctoral journey a truly enjoyable and transformative experience. I am forever grateful our paths have crossed, and I look forward to many more adventures together.

There are several people from the University of Murcia without whom I would not have embarked on a Ph.D., and I am very grateful for their pivotal roles in my life journey. Thank you Alberto Ros, for introducing me to the marvelous world of computer architecture in my sophomore year and for being a role model to this day. Thank you Mercedes Valdés, for introducing me to academic research, and for your unconditional support in all my endeavors and career aspirations. Thank you Antonio García, for your inspiring guest lecture on GPUs that ended up with me joining ARM for two years. Thanks for teaching me everything I know about RTL design and for being a great mentor and friend. Thank you for always advocating for me, before, during and after my time at ARM. Thank you Juan Luis Aragón for encouraging

me to pursue a Ph.D. program, and for your crucial support during the application process. And thanks to the UMU CS department for providing me with the solid foundation that has allowed me to get to where I am today. Muchísimas gracias.

My academic path has been intertwined with several industry experiences, and I am grateful to all the people from whom I have learned and grown along the way. Thank you to my colleagues at ARM, for the amazing time we had working together, and for all the technical and personal growth I experienced during those two years. Thank you to the AMD research team, for letting me apply my research to real-world problems, and for all the insights and experiences I gained during those internships. Thank you to my colleagues at Cerebras Systems for everything I learned about massively parallel systems, and in particular to Robert Schreiber, for being an amazing mentor and for teaching me invaluable lessons about scientific rigor and academic writing. Thank you Rob for your patience, and your continued support and encouragement during my time at Cerebras and onwards. Tack så mycket.

Last, but not least, thank you to my family for your unconditional love and encouragement throughout my life, and special thanks to my parents and my wife for always believing in me. Dad, you taught me the importance of hard work and dedication, and Mom, you taught me the importance of kindness, empathy, and staying true to myself. I am grateful for all the sacrifices you have made to raise me and my siblings, and for encouraging me to fly high and pursue my goals even when that meant being far away from home. Thank you Katriina for your constant support throughout the last seven years, for sticking with me through thick and thin, cheering me up after rejections, and celebrating my successes. Thank you for moving to three different countries to let me pursue a career, and for always looking after me. Thank you for being my life partner, my best friend, and my biggest supporter. I would not be where I am today without your unwavering support and love. Gracias por todo. Kiitos kaikesta.

This dissertation was supported in part by the National Science Foundation (NSF) award No. 1763838, and based on research sponsored by the Air Force Research Laboratory (AFRL) and Defense Advanced Research Projects Agency (DARPA) under agreement FA8650-18-2-7862.

<sup>&</sup>lt;sup>1</sup>The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of AFRL and DARPA, or the U.S. Government.

To my parents and my wife.

## Contents

|   | Abs  | tract . |                                                         | iii  |

|---|------|---------|---------------------------------------------------------|------|

|   | Ack  | nowledg | gements                                                 | v    |

|   | List | of Tab  | les                                                     | xvi  |

|   | List | of Figu | ıres                                                    | xvii |

| 1 | Inti | roduct  | ion                                                     | 1    |

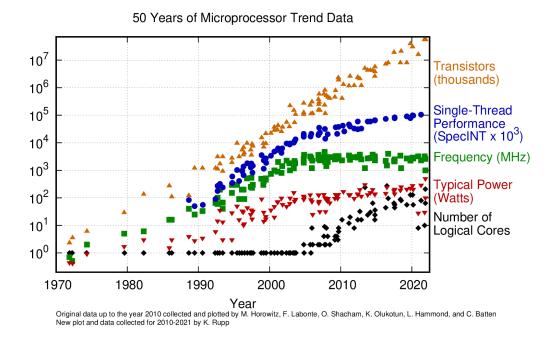

|   | 1.1  | Motiv   | ation: The Cambrian Explosion in Computer Hardware      | 2    |

|   | 1.2  | Motiv   | ation: The DECADES Project                              | 3    |

|   |      | 1.2.1   | Common Challenges in Sparse Applications                | 5    |

|   |      | 1.2.2   | Processing Sparse Applications at Scale                 | 5    |

|   | 1.3  | Thesis  | s Contributions                                         | 6    |

|   | 1.4  | Thesis  | s Outline                                               | 9    |

| 2 | Aut  | tomati  | c Generation of Formal Verification Testbenches for RTI | Ĺ    |

|   | Mo   | dule Iı | nteractions                                             | 10   |

|   | 2.1  | Introd  | luction                                                 | 11   |

|   | 2.2  | Backg   | round and Motivation                                    | 14   |

|   |      | 2.2.1   | RTL Module Interfaces                                   | 14   |

|   |      | 2.2.2   | Verifying RTL with Formal Properties                    | 15   |

|   |      | 2.2.3   | Formal Verification Engines                             | 19   |

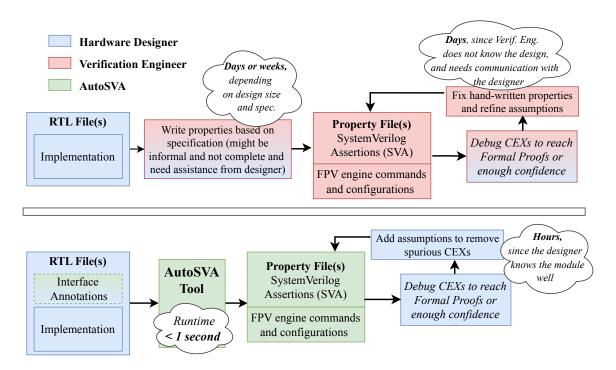

|   |      | 2.2.4   | Methodologies for RTL Verification using FPV            | 20   |

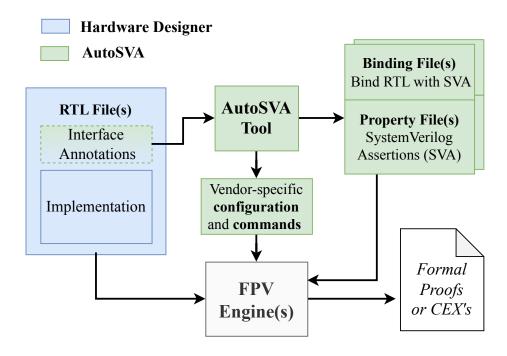

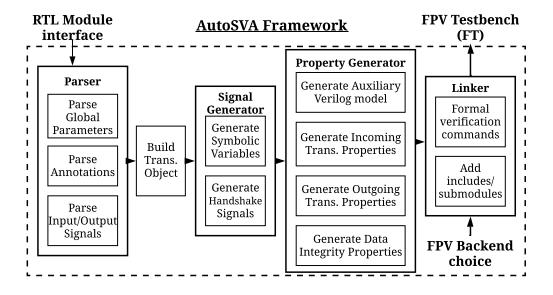

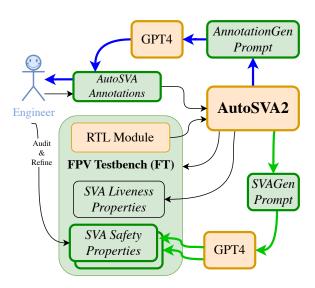

|   | 2.3 | The A   | AutoSVA Framework                                    | 22       |

|---|-----|---------|------------------------------------------------------|----------|

|   |     | 2.3.1   | The AutoSVA Interface-Annotation Language            | 24       |

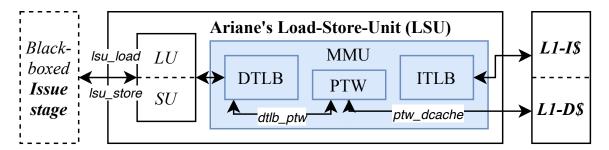

|   |     | 2.3.2   | Property Generation Based on Transaction Attributes  | 26       |

|   |     | 2.3.3   | AutoSVA Implementation and Process Steps             | 28       |

|   | 2.4 | Evalua  | ation                                                | 30       |

|   |     | 2.4.1   | Methodology                                          | 30       |

|   |     | 2.4.2   | Applying AutoSVA to RTL Modules                      | 31       |

|   |     | 2.4.3   | Results                                              | 33       |

|   | 2.5 | Chapt   | ger Summary                                          | 36       |

| 3 | Sca | lable [ | Latency-tolerance for Off-the-shelf CPUs in Manycore | <b>e</b> |

|   | SoC | Cs      |                                                      | 37       |

|   | 3.1 | Introd  | luction                                              | 37       |

|   | 3.2 | Backg   | ground and Motivation                                | 42       |

|   |     | 3.2.1   | The Need for Practical Specialization for IMAs       | 42       |

|   |     | 3.2.2   | Decoupled Access/Execute (DAE)                       | 43       |

|   |     | 3.2.3   | Prefetching                                          | 46       |

|   |     | 3.2.4   | Additional Latency Tolerance Techniques              | 47       |

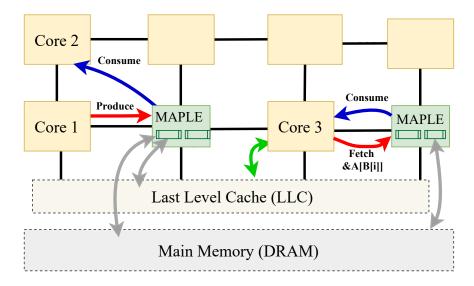

|   | 3.3 | The M   | MAPLE Hardware-Software Co-design                    | 48       |

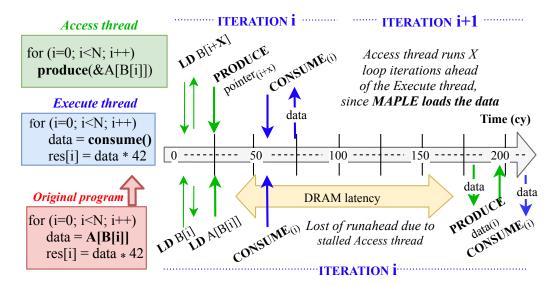

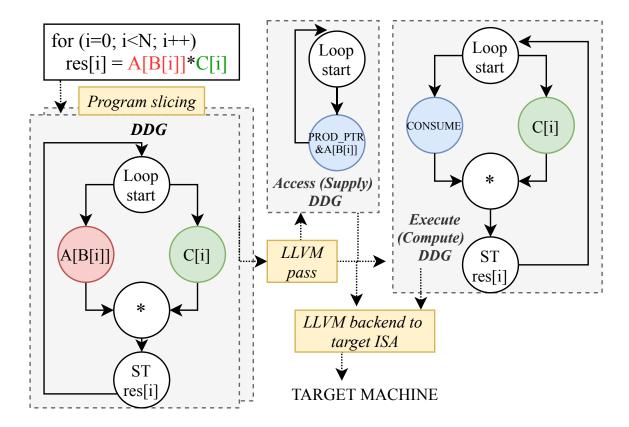

|   |     | 3.3.1   | MAPLE API for Decoupled Programs                     | 49       |

|   |     | 3.3.2   | MAPLE API for Prefetching                            | 52       |

|   |     | 3.3.3   | Targeting MAPLE Automatically                        | 53       |

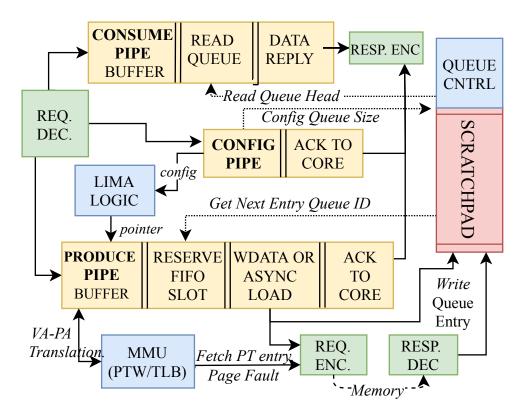

|   |     | 3.3.4   | MAPLE Hardware Implementation                        | 55       |

|   |     | 3.3.5   | Virtual Memory Support                               | 57       |

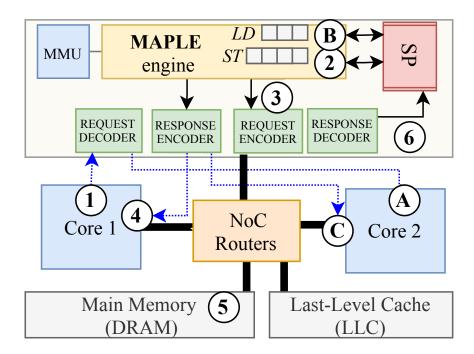

|   |     | 3.3.6   | Communicating with MAPLE units                       | 58       |

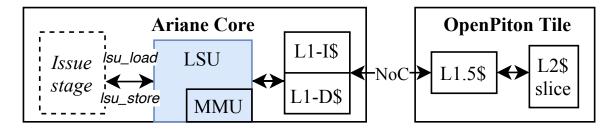

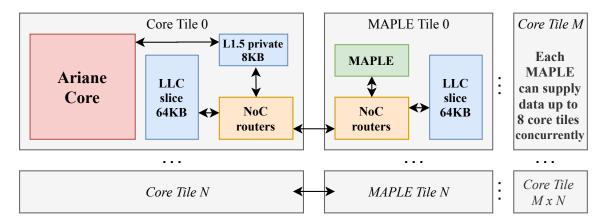

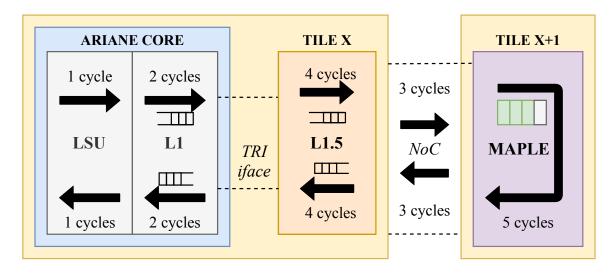

|   |     | 3.3.7   | MAPLE Integration via NoC                            | 59       |

|   |     | 3.3.8   | Reusing MAPLE in SoCs                                | 60       |

|   |     | 3.3.9   | Formal Verification of MAPLE                         | 61       |

|   | 3.4 | Evalua | ation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61        |

|---|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |     | 3.4.1  | Applications for Data-analytics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62        |

|   |     | 3.4.2  | FPGA Emulated SoC System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63        |

|   |     | 3.4.3  | Evaluation Against Prior Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65        |

|   |     | 3.4.4  | Sensitivity Parameters to Characterize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65        |

|   | 3.5 | Result | SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66        |

|   |     | 3.5.1  | FPGA Emulation of the SoC Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66        |

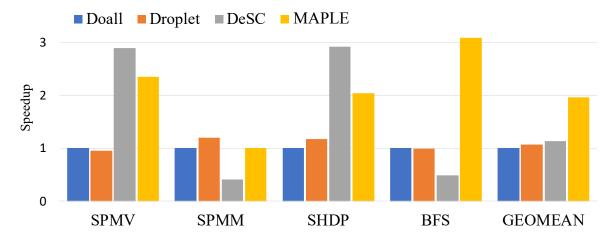

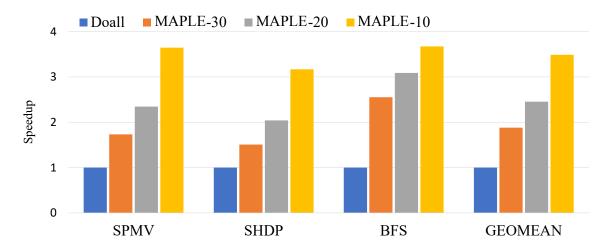

|   |     | 3.5.2  | Comparison against Prior Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70        |

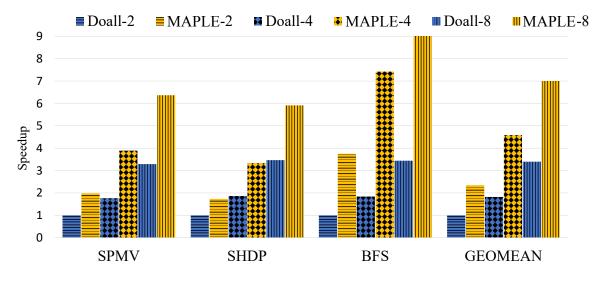

|   |     | 3.5.3  | Conclusions about the Sensitivity Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71        |

|   |     | 3.5.4  | Area analysis of the RTL Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73        |

|   | 3.6 | Chapt  | er Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74        |

| 4 | A T | )-+- C | and the Theorem 1 and 1 and 1 and 1 and 2 |           |

| 4 |     |        | entric Execution Model and Architecture for Sparse Ap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

|   | -   | ations |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>75</b> |

|   | 4.1 |        | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76        |

|   | 4.2 | Backg  | round and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82        |

|   |     | 4.2.1  | Sparse Data Structures and their Pointer Indirection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82        |

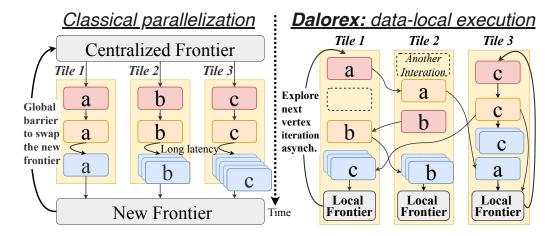

|   |     | 4.2.2  | Bulk Synchronous Parallelization (BSP) of Graph Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83        |

|   |     | 4.2.3  | Prior Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85        |

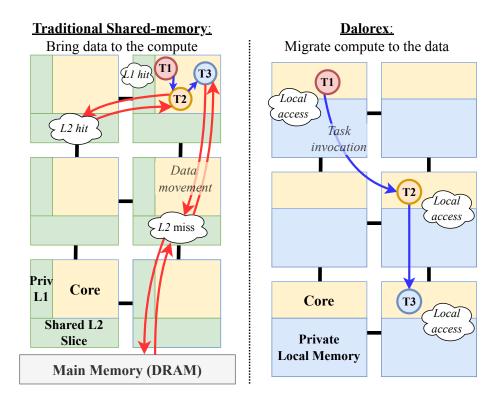

|   | 4.3 | The D  | Oata-Centric Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88        |

|   |     | 4.3.1  | Data distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89        |

|   |     | 4.3.2  | Programming model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89        |

|   |     | 4.3.3  | Program Flow and Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90        |

|   | 4.4 | Hardw  | vare Support for the Data-Centric Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94        |

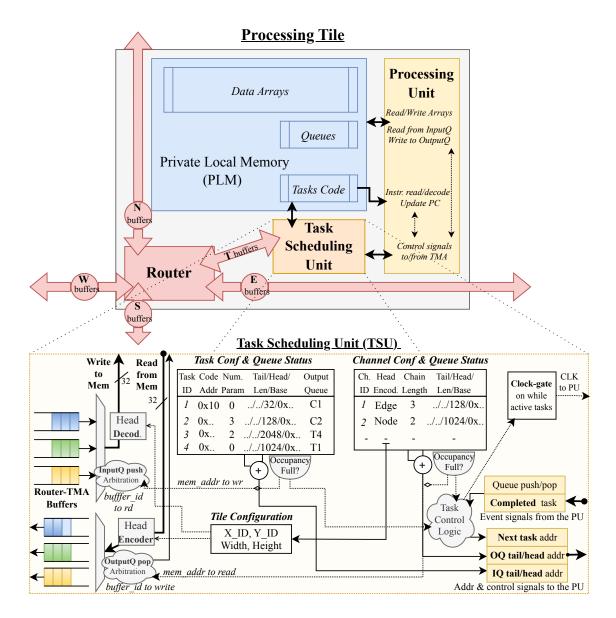

|   |     | 4.4.1  | The Task Scheduling Unit (TSU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 96        |

|   |     | 4.4.2  | Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97        |

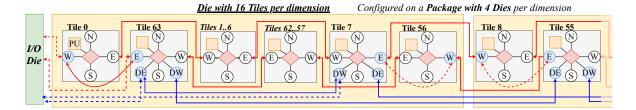

|   |     | 4.4.3  | Communication Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99        |

|   |     | 4.4.4  | Software-configurable Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100       |

|   | 4.5 | Tasca                      | de Hardware Support for Reductions                       | 102 |  |  |  |  |

|---|-----|----------------------------|----------------------------------------------------------|-----|--|--|--|--|

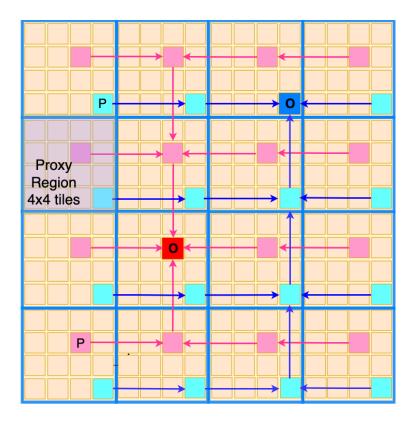

|   |     | 4.5.1                      | Proxy Tasks                                              | 104 |  |  |  |  |

|   |     | 4.5.2                      | Proxy Cache Design                                       | 106 |  |  |  |  |

|   |     | 4.5.3                      | Cascading                                                | 110 |  |  |  |  |

|   | 4.6 | Evalua                     | ation Methodology                                        | 112 |  |  |  |  |

|   |     | 4.6.1                      | Applications and Datasets                                | 112 |  |  |  |  |

|   |     | 4.6.2                      | Simulator Framework                                      | 113 |  |  |  |  |

|   |     | 4.6.3                      | Comparing with the State-of-the-Art                      | 115 |  |  |  |  |

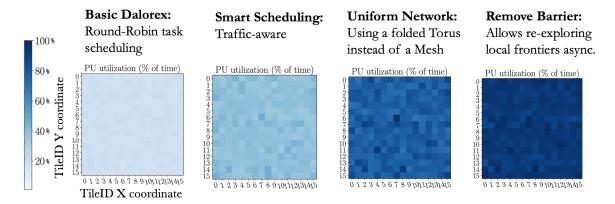

|   |     | 4.6.4                      | Design Characterization                                  | 116 |  |  |  |  |

|   | 4.7 | Result                     | ts                                                       | 117 |  |  |  |  |

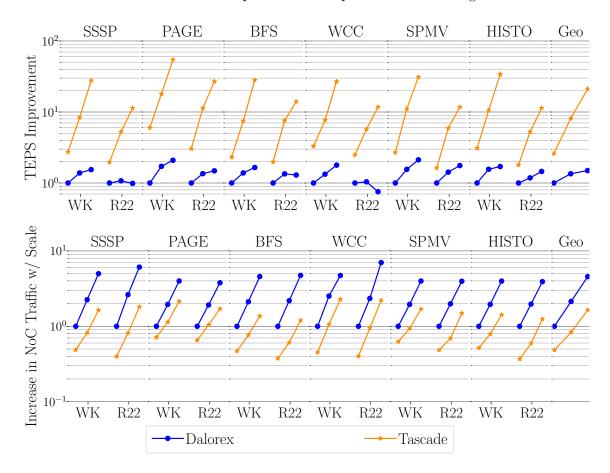

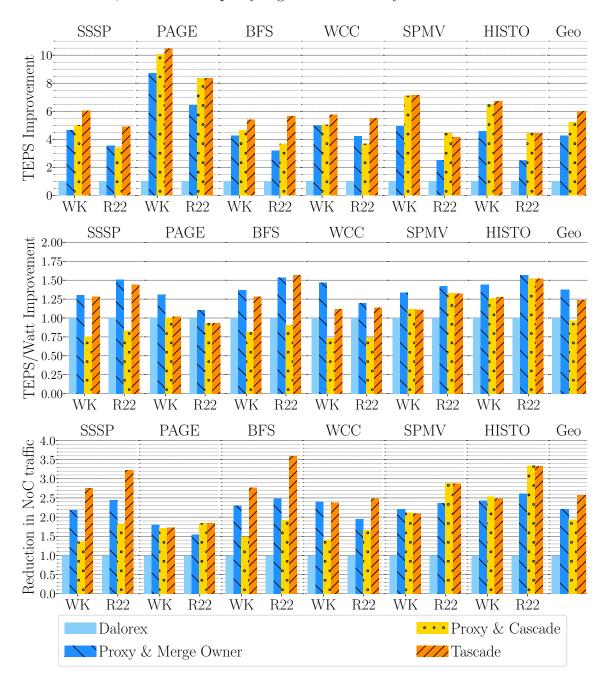

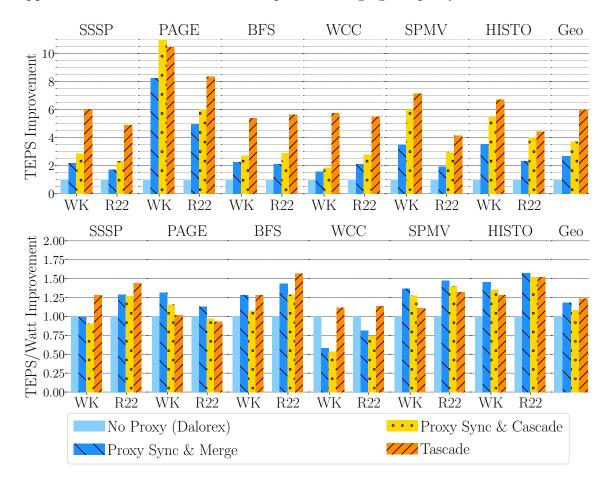

|   |     | 4.7.1                      | Evaluating Proxy Caching and Cascading                   | 119 |  |  |  |  |

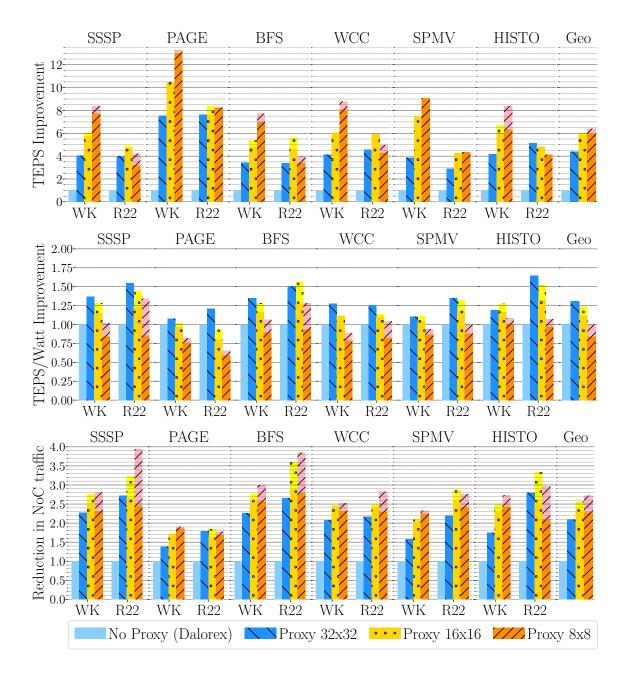

|   |     | 4.7.2                      | Optimal Proxy Region Size                                | 122 |  |  |  |  |

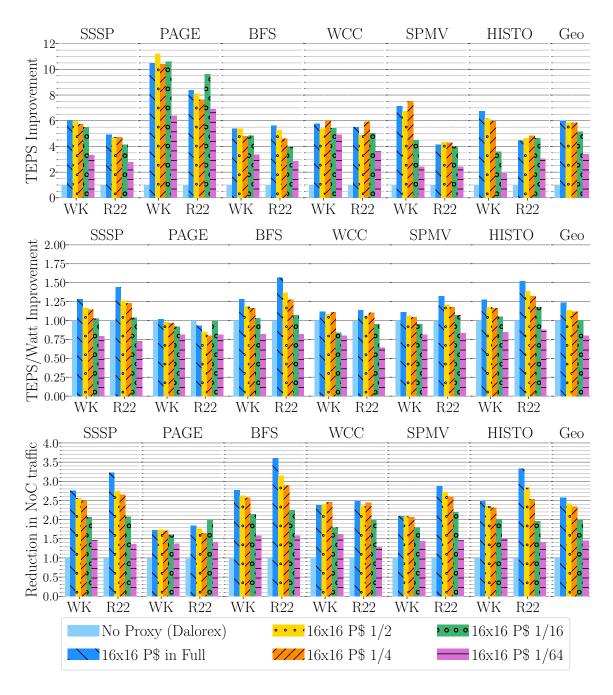

|   |     | 4.7.3                      | Impact of Limiting Proxy Cache Capacity                  | 124 |  |  |  |  |

|   |     | 4.7.4                      | The Benefits of Asynchrony                               | 125 |  |  |  |  |

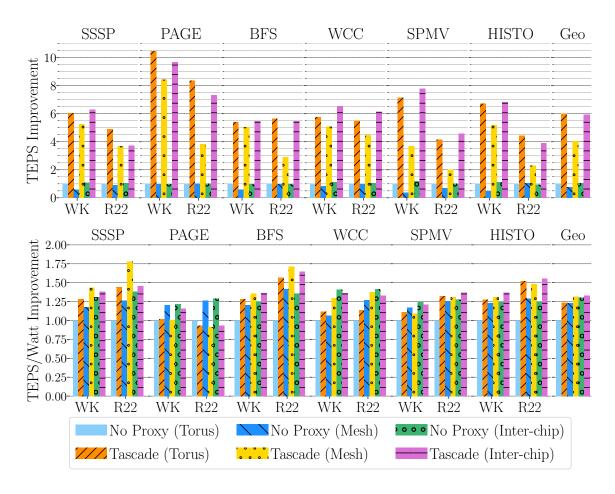

|   |     | 4.7.5                      | Impact of the NoC Design Choice                          | 127 |  |  |  |  |

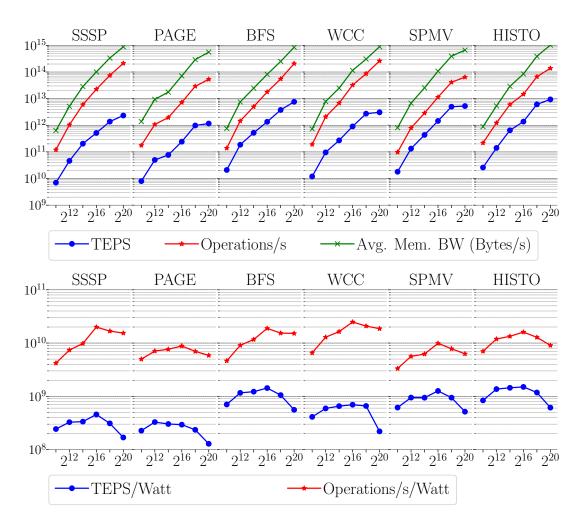

|   |     | 4.7.6                      | Strong Scaling Up to a Million Tiles                     | 129 |  |  |  |  |

|   | 4.8 | Chapt                      | ter Summary                                              | 133 |  |  |  |  |

| 5 | Con | Conclusion and Future Work |                                                          |     |  |  |  |  |

|   | 5.1 | Contri                     | ibutions and Conclusions                                 | 134 |  |  |  |  |

|   | 5.2 | Future                     | e Work                                                   | 139 |  |  |  |  |

|   |     | 5.2.1                      | Extending the Coverage of Automatically Generated Formal |     |  |  |  |  |

|   |     |                            | Properties                                               | 139 |  |  |  |  |

|   |     | 5.2.2                      | Using FPV to Harness LLM-generated RTL                   | 140 |  |  |  |  |

|   |     | 5.2.3                      | Large-scale Parallel Architectures for Sparsity in AI    | 141 |  |  |  |  |

|   |     | 5.2.4                      | Dynamic Address-space Mapping for Improved Work-balance  |     |  |  |  |  |

|   |     |                            | in Data-centric Architectures                            | 141 |  |  |  |  |

| Bibliog | graphy |                                                                | 144 |

|---------|--------|----------------------------------------------------------------|-----|

| 5.3     | Summ   | ary                                                            | 143 |

|         |        | Modularity                                                     | 142 |

|         | 5.2.5  | Hardware-software Interfaces in Chiplets for System-in-Package |     |

## List of Tables

| 2.1 | The AutoSVA language. Constants are written in lowercase and syntax     |     |

|-----|-------------------------------------------------------------------------|-----|

|     | in uppercase. STR and ASSIGN are Verilog's syntax for strings and       |     |

|     | assignments                                                             | 25  |

| 2.2 | Properties generated for each transaction attribute. Attributes marked  |     |

|     | with * generate properties that are asserted when the transaction is    |     |

|     | incoming and assumed when outgoing                                      | 26  |

| 2.3 | RTL modules tested with AutoSVA. Ariane modules are indicated with      |     |

|     | A, and OpenPiton with O. The issue numbers refer to the upstream        |     |

|     | Ariane repository [123]                                                 | 33  |

| 3.1 | Classification of the hardware-assisted prior work on IMA latency miti- |     |